We Broke Google's CoralNPU — And Then We Fixed It

At ChipForge, we're building the world's first decentralized chip design ecosystem. As part of that effort, we're actively working on our own Neural Processing Unit (NPU).

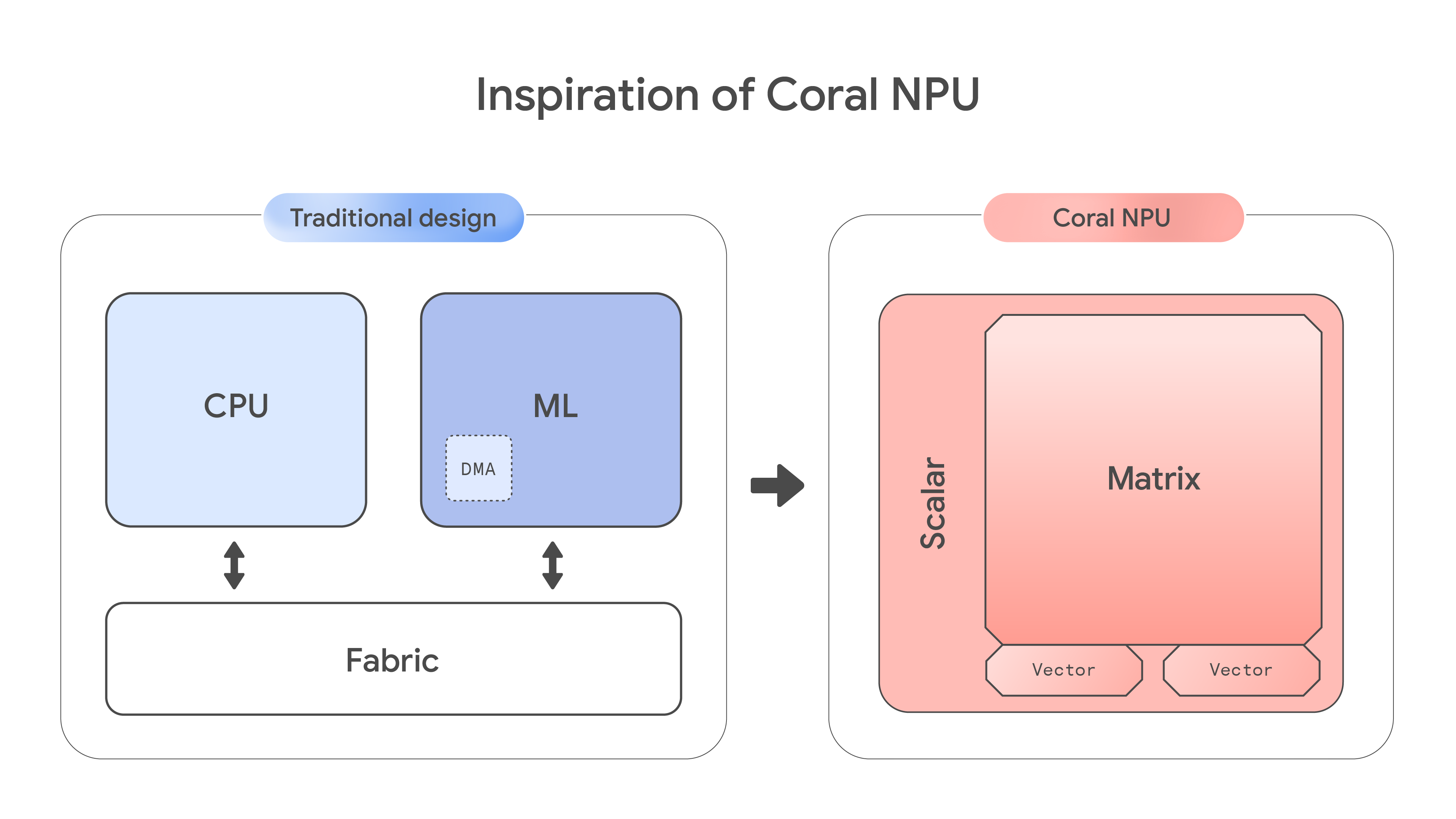

Instead of starting from scratch, we chose CoralNPU as our baseline and decided to build on top of it.

But before asking anyone else to improve the design, we had to answer a hard question first:

Is the current design actually correct?

Building a Verification Pipeline

So we built a strong validation and verification pipeline — one capable of fully verifying real hardware designs, including future submissions from external contributors and miners.

This wasn't just about testing. We needed to prove correctness at the RTL level, catch edge cases, and ensure timing constraints would hold in real silicon.

The Tools We Used

Our verification stack includes:

- Verilator for fast simulation

- Cocotb for Python-based testbenches

- Yosys for synthesis verification

- OpenLane for full PPA analysis

What We Found

Within five weeks, our pipeline uncovered multiple critical issues in the original CoralNPU design:

- Memory controller race condition — Under specific burst patterns, the memory controller could enter a deadlock state

- Accumulator overflow — The MAC unit didn't properly handle overflow in edge cases

- Clock domain crossing issue — Metastability risk in the configuration interface

The Fixes

We didn't just report these issues — we fixed them. Each fix was:

- Properly root-caused with waveform analysis

- Tested with targeted regression tests

- Verified not to introduce new timing violations

- Documented for upstream contribution

Contributing Back

All our fixes have been submitted upstream to the CoralNPU repository. This is what decentralized chip design looks like:

- Open verification pipelines

- Community-driven improvements

- Shared benefits for everyone

What's Next

This is just the beginning. Our NPU design challenges on ChipForge will build on this foundation, inviting engineers worldwide to compete on improving neural accelerator designs.

The best designs will be:

- Validated by our proven verification pipeline

- Ranked by PPA (Power, Performance, Area) metrics

- Rewarded with TAO tokens

- Eventually fabricated into real silicon

Want to contribute?

Join our network of engineers building the future of chip design.